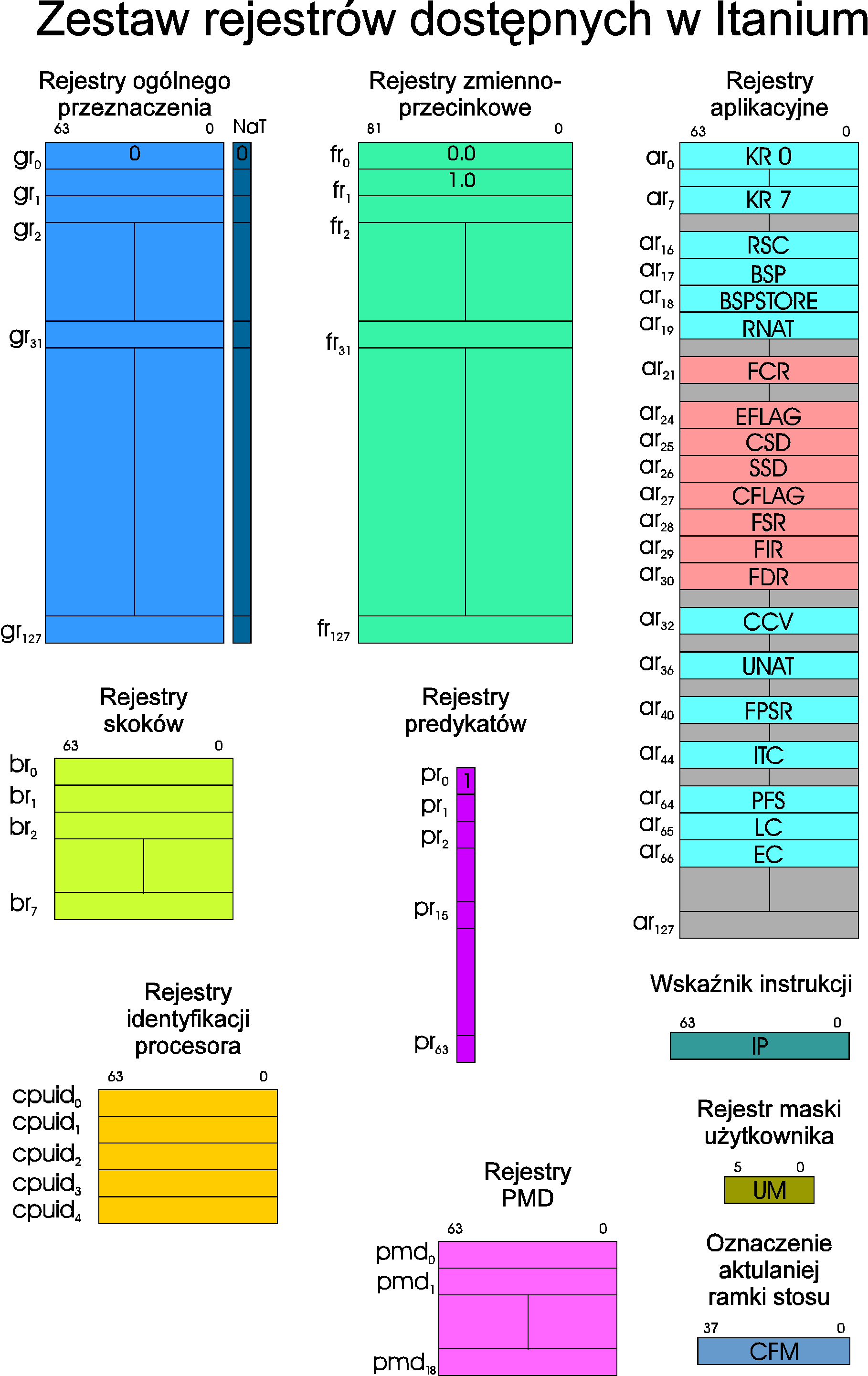

Rozkład rejestrów w Itanium

W procesorze Itanium ilość rejestrów przedstawia się następująco:

Rejestry ogólnego przeznaczenia – 128 sztuk, adresowane od rejestru GR[0], który jest tylko do odczytu, do rejestru GR[127]. Rejestry od GR[0] do GR[31] to rejestry statyczne, natomiast rejestry od GR[32] do GR[127] to rejestry rotujące

Rejestry NaT – 128 sztuk, po jednym rejestrze NaT do każdego rejestru ogólnego przeznaczenia.

Rejestry Zmiennoprzecinkowe – 128 sztuk, adresowane od rejestru FP[0], który wraz z rejestrem FP[1] są tylko do odczytu. Rejestry od FP[0] do FP[31] to rejestry statyczne, natomiast rejestry od FP[32] do FP[127] to rejestry rotujące.

Rejestry Aplikacyjne – 128 sztuk

Rejestry Predykatów – 64 sztuki. Rejestr PR[0] jest tylko do odczytu. Rejestry od PR[0] do PR[15] to rejestry statyczne, natomiast od PR[16] do PR[63] to rejestry rotujące.

Rejestry Skoków – 8 sztuk.

Wskaźnik Instrukcji – Jeden 64-bitowy rejestr.

Oznaczenie Aktualnej Ramki Stosu – Zestaw rejestrów zajmujący 38 bitów.

Rejestry PMD – 18 sztuk.

Rejestry od 0 do 3 to tzw. rejestry statusu przepełnienia (Performance Contuer Overflow Status Registers).

Rejestry 4-7 to tzw. rejestry ogólne rejestry badania osiągów (Preformance Contuer Configuration/Data Registers), w rejestrach tych znajdują się zarówno części związane z konfigurajcą (PMC) jak i właściwe rejestry PMD przechowujące dane.

Rejestry 8-9 to rejestry (Opcode Match Registers)

Rejestry 10-11 to tzw. rejestry konfiguracji zdarzeń systemowych (Instruction/Data Event Addres Configuration Registers)

Rejestry danych zdarzeń systemowych zajmują (jeśli procesor jest w tym trybie badania konfiguracji) miejsca 0-3 oraz 17.

Rejestr 12 to tzw. rejestr konfiguracji skoków krokowych (Branch Trace Buffer Confguration Register)

Rejestru danych skoków krokowych zajmują (jeśli procesor jest w tym trybie badania konfiguracji) miejsca 8-16

Rejestr 13 to tzw. rejestr sprawdzania zasięgu adresu (IA-64 Instruction Address Range Check Register)

Rejestr Maski Użytkownika – Jeden rejestr składający się z pięciu 1-bitowych flag.

Rejestry Identyfikacji Procesora – 5 rejestrów.

Liczba podstawowych rejestrów raczej będzie taka sama także i w innych procesorach serii IA-64. Gdyby się wzrosła ilość rejestrów ogólnego przeznaczenia, lub zmienno-przecinkowych, musiało by to pociągać za sobą zmianę długości instrukcji, ponieważ zestaw 128 bitowych rejestrów jest adresowany za pomocą 7 bitów, gdyby ta liczba wzrosła adres musiał by zawierać co najmniej 8 bitów co by wiązało się ze zwiększeniem długości instrukcji o średnio 3 bity.

W procesorach innych niż Itanium prawdopodobne są jednakże rozszerzenia w zestawie Rejestrów Aplikacyjnych który to zestaw posiada wiele pól ignorowanych lub zarezerwowanych. Możliwa jest także zmiana ilości rejestrów identyfikacji procesora, gdzie nawet explicite jest podane ile tych rejestrów posiada odpowiedni procesor w cpuid[3]. Do tej pory nie zdołaliśmy się zorientować w ile rejestrów PMD został wyposażony procesor Itanium.

Wracając jeszcze do rejestrów, lub części rejestrów, które są zarezerwowane, lub ignorowane, to takie miejsca występują nie tylko w rejestrach Aplikacyjnych i miejsca te mogą być w przyszłości wykorzystane.

komentarze

Copyright © 2008-2010 EPrace oraz autorzy prac.